Reference:

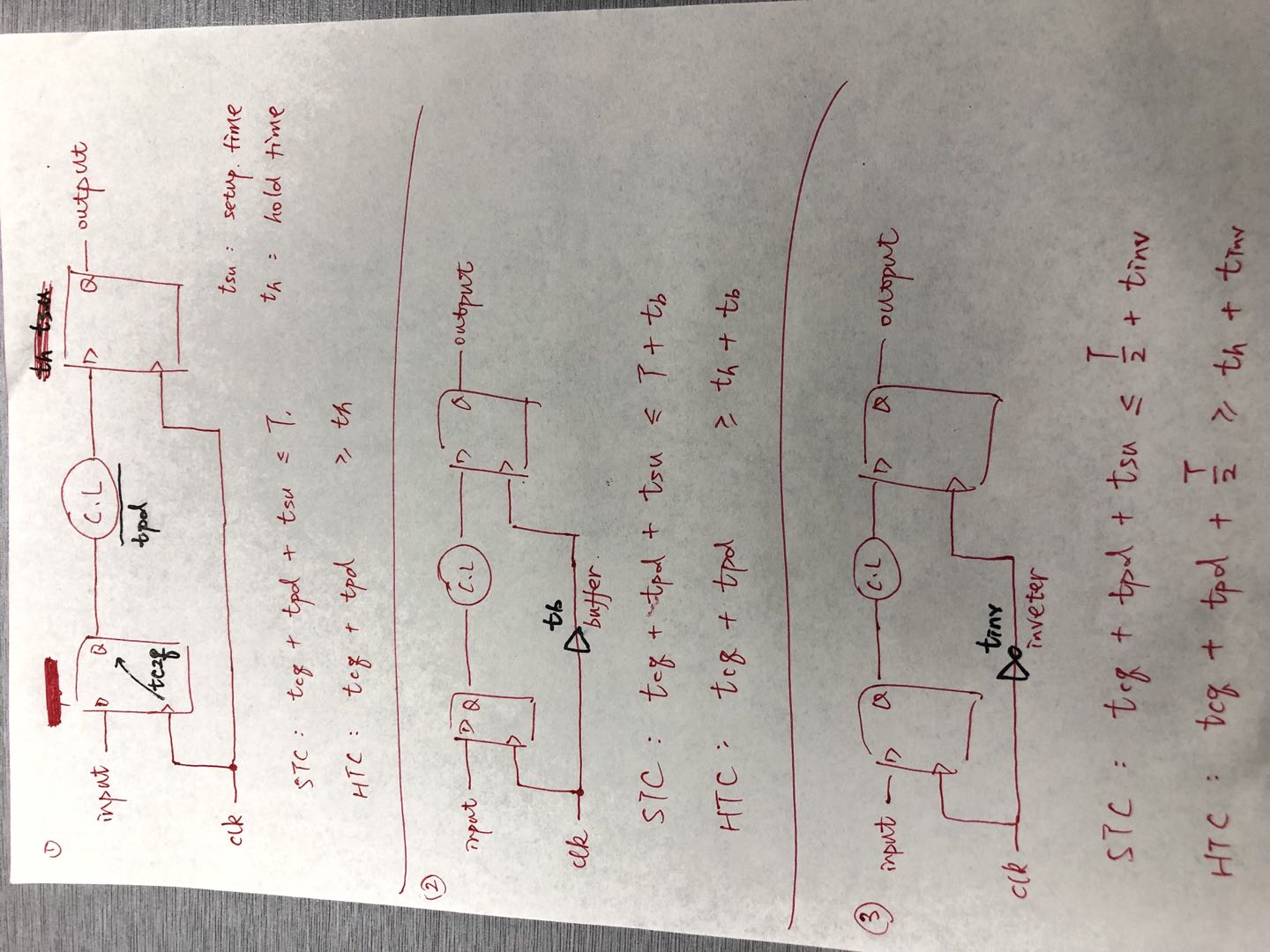

STC: max delay in data path; min delay in clock path

HTC: min delay in data path; max delay in clock path

前六种方法是相对应的

How to fix setup violations?

Reduce Tcq, Tpd, Tsu; Increase Tclock

-

Increase the drive strength of data-path logic gates

-

Use the data-path cells with lesser threshold voltages (HVT RVT/SVT LVT)

-

Improve the setup time of capturing flip-flop

-

Insert buffer in the clock path

-

Reduce tcq of launching flip-flop

- Improve transition at flip-flops clock pin

- Choose a flip-flop of high drive strength. However, if by doing so, clock transition degrades, delay can actually increase

- Replace the flip-flop with a flip-flop of same drive strength, but lower Vth

-

Postive clock skew helps improve the setup slack

- Increase the clock latency of capturing flip-flop

- Decrease the clock latency of launching flip-flop

-

Increase clock period (Reduce frequency of design)

-

Add repeaters

-

Restructuring of the data path

-

Routing topologies

- less net delay (backend route)

- try the net to have as less detouring as possible

- Vias increase the net resistance. So, try to have as less vias as possible

- Higher metal layers have less resistance. So, long nets can be routed in higher layers to have less net delay

How to fix hold violations?

Increase Tcq, Tpd; Reduce Th

-

Reduce the drive strength of data-path logic gates

-

Use the data-path cells with higher threshold voltages (HVT RVT/SVT LVT)

-

Improve the hold time of capturing flip-flop

- Using a capturing flip-flop with higher drive strength and/or lower threshold voltage

- Improving the transition at flip-flop clock pin

-

Insert delay elements(ex. buffer) in the data path

-

Increase tcq of launching flip-flop

- Decrease the drive strength of the flip-flop

- Higher threshold voltage(Vth) of the flip-flop

-

Negative clock skew helps aids hold timing

- Decrease the clock latency of capturing flip-flop

- Increase the clock latency of launching flip-flop

-

Detoured routing